#### ENERGY-EFFICIENT I/O INTERFACE DESIGN WITH ADAPTIVE POWER-SUPPLY REGULATION

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> Gu-Yeon Wei June 2001

© Copyright by Gu-Yeon Wei 2001

All Rights Reserved

# Abstract

The demand for high-bandwidth and low-power I/O interfaces for intra-chip communication motivates this work. Aggressive CMOS scaling has enabled higher performance and integration at the expense of higher power dissipation and design complexity. This work investigates a technique that adaptively regulates the supply voltage to minimize power consumption while enabling a simpler I/O design.

Adaptively regulating the supply voltage offers significant energy savings due to energy's squared dependence on voltage for digital circuits. In order to find the minimum voltage required for proper operation at speed, a digital power-supply regulator relies on an inverter-based model of the worst-case critical path and the model's ability to track the delay of the critical path with respect to process and environmental conditions. A purely digital implementation leads to a robust design that can also benefit from the same power savings technique as in the load. An experimental prototype demonstrates conversion efficiencies greater than 90-% across a wide range of regulated voltage levels.

A high-speed parallel I/O interface driven with an adaptively regulated supply can take advantage of several properties that lead to a simple, low-power solution. In addition to minimizing power consumption, given the tracking ability of the inverter-based model of the critical path, the regulated voltage level contains information about process and operating conditions. This property allows the designer to replace precision analog circuits with simple digital gates and results in a simpler design. Furthermore, it enables a receiver design whose bandwidth tracks the bit rate and a transmitter with automatic slew-rate control. A parallel I/O prototype with adaptive power supply regulation was fabricated in a  $0.35\mu m$  CMOS technology. The prototype achieves 0.2-0.8 Gb/s link operation and its power consumption is a function of the bit rate to a power greater than two.

# Acknowledgments

Looking back on the nineties at Stanford, I fondly remember many wonderful experiences and friendships. Stanford has a dynamic collection of students, teachers, and staff that encourages one to pursue knowledge in an exciting environment. I will always cherish my time here.

I am indebted to my adviser, Professor Mark Horowitz, who was kind enough to support a clueless undergraduate to do research one summer in 1994. Little did he know that it would last more than six years. I thank Mark for his keen insight, guidance, and patience throughout the course of my research and thesis. I feel incredibly fortunate to have had him as my adviser.

I would also like to thank Professor Bruce Wooley for being my associate adviser, serving on my orals committee, reading this thesis, and continued support throughout the years in CIS. I am grateful to Professor James Harris and Professor Bob Dutton for also having served on my orals examination committee. I also extend thanks to Professor Jim Plummer for being my undergraduate adviser and giving me an opportunity to play in the clean room for a summer. I am also fortunate to have received technical wisdom and guidance from Professor Tom Lee.

This research and thesis could not have been possible without the collaboration, encouragement, and aid of many colleagues. I especially thank Stefanos Sidiropoulos for his generous help and guidance throughout the design and layout of the test chip and for reading this thesis. This work also would not have been possible if it were not for the hard work and dedication of Dean Liu and Jaeha Kim. I am grateful for the discussions and camaraderie of fellow students, past and present: Dan Weinlader, Birdy Amrutur, Ron Ho, Ken Mai, Ken Yang, Ricardo Gonzalez, John Maneatis, Arvin Shahani, Derek Shaeffer, Bennett Wilburn, Patrick Yue, Tom Soh, Adrian Ong, Joe Ingino, and all of the students in the Wooley, Horowitz and Lee groups.

Outside of school life, I have many people to thank for their continued support and friendship. Dan Kim, Woo-Young Rhee, Stephen Ryu, Jaeson Kim, Jay Kim, James Yao, Charles Watson, K.C. Chang and Eugene Jhong have enriched my graduate school years. Kenny Park, Eddie Ahn, David Kim, Jeehun Hwang, Christian Gehman, Steve Martinez, Dave Atkins, and countless others have made my undergraduate years memorable. I also thank Jin Lee for her friendship and support through the last stretch.

Throughout my life, my parents have always supported me with love and prayer. I dedicate this thesis to them. I am also fortunate to have had three sisters who watched over their little brother. Lastly, I am grateful for my nieces and nephew, who were always so loving and cheerful.

# **Table of Contents**

| Abstrac   | ct                                                                    | V   |

|-----------|-----------------------------------------------------------------------|-----|

| Acknow    | vledgments                                                            | vii |

| List of ] | Figures                                                               | xi  |

| List of 7 | Tables                                                                | XV  |

| Chapte    | r 1 Introduction                                                      | 1   |

| 1.1       | Low-Power Techniques                                                  |     |

| 1.2       |                                                                       |     |

| 1.3       | Organization                                                          | 4   |

| Chapte    | r 2 Background                                                        | 7   |

| 2.1       | Power and Delay in Digital CMOS Circuits                              | 8   |

| 2.2       | Delay Tracking                                                        | 14  |

|           | 2.2.1 Inverter-based tracking                                         |     |

|           | 2.2.2 Other non-ideal effects                                         |     |

|           | 2.2.3 Delay Tracking Summary                                          |     |

| 2.3       | I I I J 8                                                             |     |

|           | <ul><li>2.3.1 Buck Converter</li><li>2.3.2 PID Control Loop</li></ul> |     |

| 2.4       | -                                                                     |     |

| Chapte    | r 3 Digital Power-Supply Controller                                   |     |

| 3.1       | A/D Conversion                                                        |     |

| 3.2       |                                                                       |     |

| 3.3       | 0                                                                     |     |

| 3.4       | · ·                                                                   |     |

| 3.5       |                                                                       |     |

| 3.6       | Summary                                                               | 54  |

| Chapter | : 4 I/O | Interface Design                           |     |

|---------|---------|--------------------------------------------|-----|

| 4.1     | Overv   | iew of parallel links                      |     |

|         | 4.1.1   | Critical-path delay                        | 60  |

|         | 4.1.2   | Signal Integrity                           | 62  |

| 4.2     | Findin  | g the "right" voltage                      | 63  |

|         | 4.2.1   | Summary                                    |     |

| 4.3     | Transr  | nitter Design                              | 77  |

|         | 4.3.1   | High-Impedance Drivers                     |     |

|         | 4.3.2   | Impedance, Current and Slew-Rate Control   |     |

|         | 4.3.3   | Transmitter Summary                        |     |

| 4.4     | Receiv  | ver Design                                 |     |

|         | 4.4.1   | Bandwidth-Tracking Preamplifier            |     |

|         | 4.4.2   | Regenerative Latch and Timing              |     |

|         | 4.4.3   | Receiver Summary                           |     |

| 4.5     | Timin   | g Recovery                                 |     |

|         | 4.5.1   | Dual-loop architecture                     |     |

|         | 4.5.2   | Digital interpolation                      |     |

|         | 4.5.3   | Duty-cycle adjuster                        |     |

|         | 4.5.4   | Clock Distribution and Relative Timing     |     |

|         | 4.5.5   | Timing Recovery Summary                    |     |

| 4.6     | Experi  | imental Results                            | 100 |

|         | 4.6.1   | Test-chip Components and Testing Circuitry |     |

|         | 4.6.2   | Dual-Loop DLL                              |     |

|         | 4.6.3   | I/O Transceiver                            | 105 |

|         | 4.6.4   | Power Breakdown Analysis                   | 108 |

| 4.7     | Summ    | ary                                        | 110 |

|         | - 0     |                                            |     |

| Chapter | s 5 Con | iclusions                                  |     |

| Referen | Ces     | •••••••••••••••••••••••••••••••••••••••    |     |

|         |         | • • • • • • • • • • • • • • • • • • • •    |     |

Х

# **List of Figures**

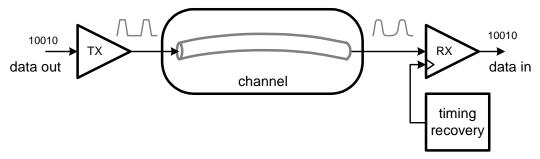

| Figure 1.1.  | Link components                                                                                                 | 4    |

|--------------|-----------------------------------------------------------------------------------------------------------------|------|

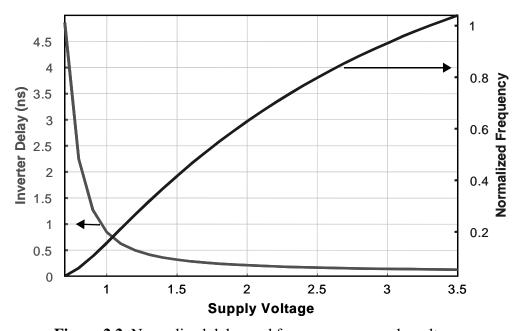

| Figure 2.2.  | Normalized delay and frequency vs. supply voltage                                                               | 9    |

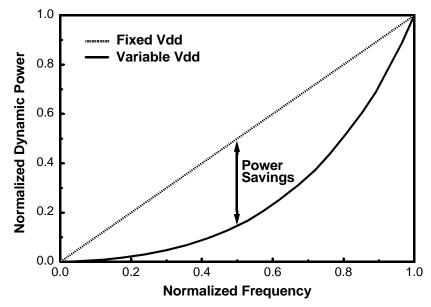

| Figure 2.3.  | Normalized power vs. normalized frequency                                                                       | 9    |

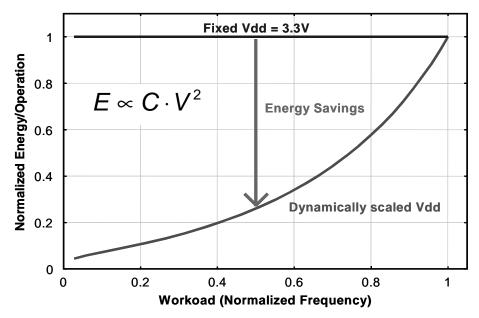

| Figure 2.4.  | Normalized energy vs. normalized frequency                                                                      | 10   |

| Figure 2.5.  | Normalized frequency vs. supply voltage vs. corners                                                             | 11   |

| Figure 2.6.  | Normalized energy vs. normalized frequency vs. corners                                                          | 12   |

| Figure 2.7.  | Normalized frequency vs. supply voltage vs. temperature                                                         | 13   |

| Figure 2.8.  | Normalized delay tracking of various complex static and dynamic ga<br>process corner                            |      |

| Figure 2.9.  | Normalized delay tracking of various complex static and dynamic ga<br>vs. temperature                           | ates |

| Figure 2.10. | Delay tracking of various static and complex gates normalized to L <sub>m</sub> FO4 inverter vs. supply voltage |      |

| Figure 2.11. | Delay tracking of various static and complex gates normalized to 1.5 FO4 inverter vs. supply voltage            |      |

| Figure 2.12. | Wire delay test bench and RC model                                                                              | 19   |

| Figure 2.13. | Wire delay tracking vs. supply voltage                                                                          | 19   |

| Figure 2.14. | Normalized effective inverter gate capacitance vs. supply voltage                                               | 20   |

| Figure 2.15. | Buck converter                                                                                                  | 23   |

| Figure 2.16. | Buck converter switching transistor power loss vs. width                                                        | 25   |

| Figure 2.17. | Control-loop block diagram                                                                                      | 26   |

| Figure 2.18. | PID control-loop frequency-domain model                                                                         | 27   |

| Figure 2.19. | PID control open-loop frequency response                                                                        |      |

| Figure 2.20. | PWM rectangular wave generation                                                                                 | 29   |

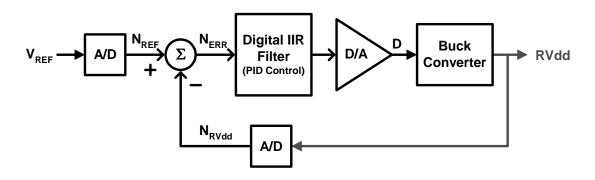

| Figure 3.1.  | Digital controller block diagram                                                                                | 31   |

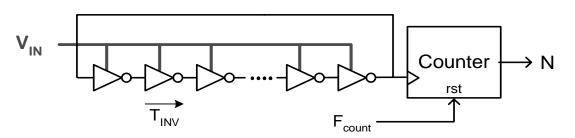

| Figure 3.2.  | Ring oscillator and counter based A/D converter                                                                 | 32   |

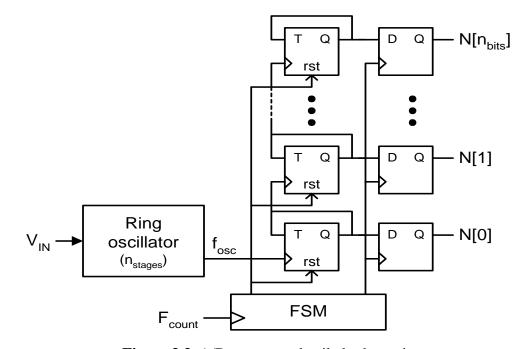

| Figure 3.3.  | A/D converter detailed schematic                                                                                | 33   |

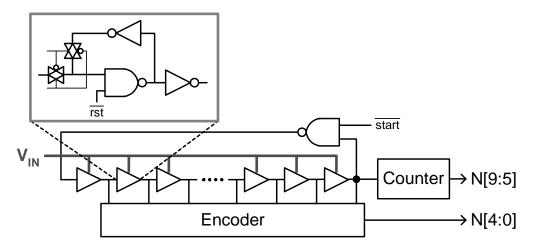

| Figure 3.4.  | Low-power A/D converter                                                                                         | 35   |

| Figure 3.5.  | Circuit implementation of PID control blocks                                                                    | 37   |

| Figure 3.6.  | Digital PID control loop                                           | 39 |

|--------------|--------------------------------------------------------------------|----|

| Figure 3.7.  | Normalized power breakdown                                         | 41 |

| Figure 3.8.  | Normalized frequency shifting                                      | 42 |

| Figure 3.9.  | Simulated open-loop response at high and low loop-frequency limits | 43 |

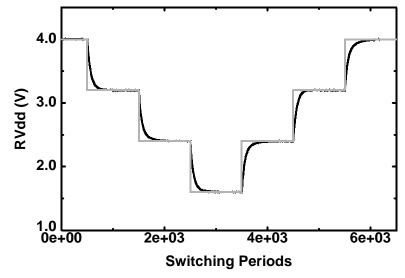

| Figure 3.10. | Simulated voltage-transient response                               | 43 |

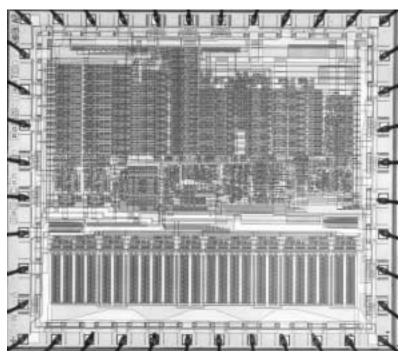

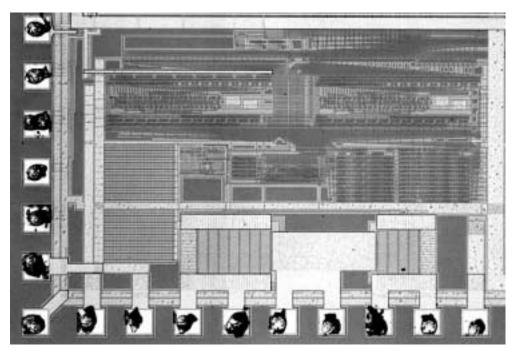

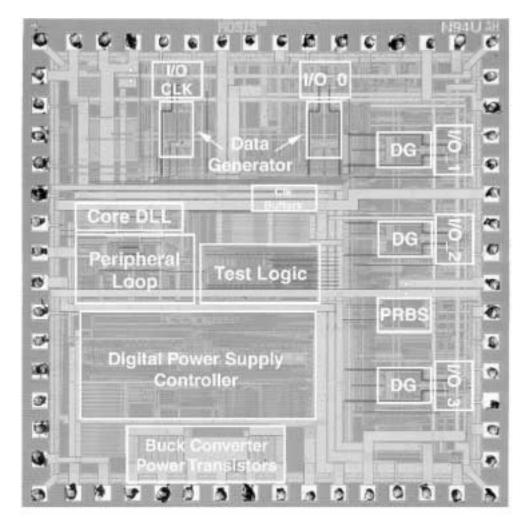

| Figure 3.11. | Test-chip micrograph                                               | 44 |

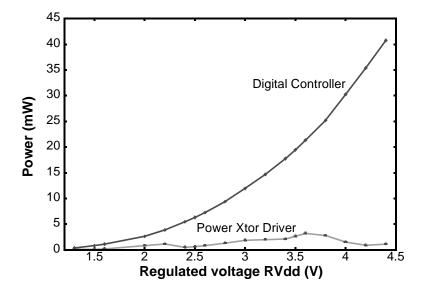

| Figure 3.12. | Overhead power vs. regulated voltage                               | 44 |

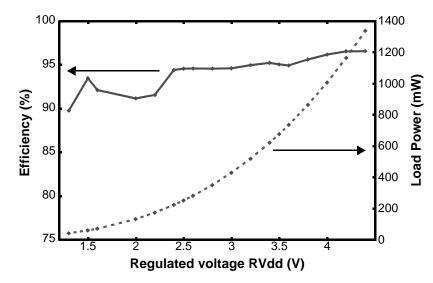

| Figure 3.13. | Conversion efficiency vs. regulated voltage                        | 45 |

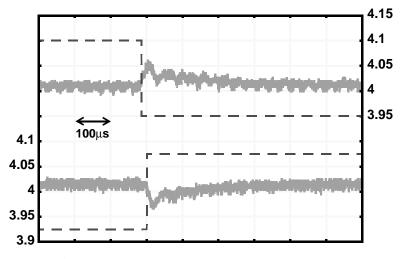

| Figure 3.14. | Measured load transient response                                   | 46 |

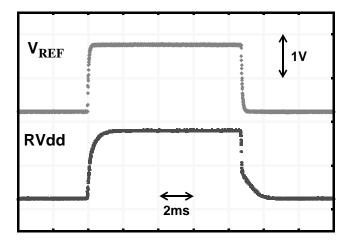

| Figure 3.15. | Measured voltage transient response                                | 46 |

| Figure 3.16. | Low-power D/A block diagram                                        | 48 |

| Figure 3.17. | Low-power controller block diagram                                 | 49 |

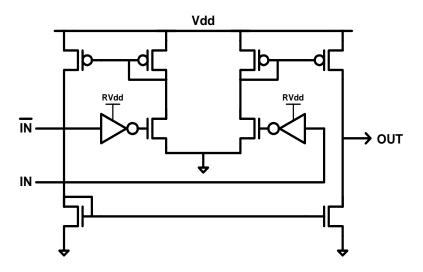

| Figure 3.18. | Low-to-high voltage converter                                      | 50 |

| Figure 3.19. | Power-supply controller block photo micrograph (zoom)              | 51 |

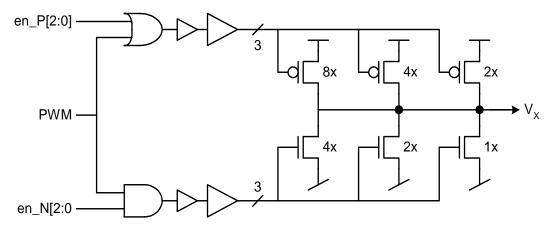

| Figure 3.20. | Segmented buck converter switching transistors                     | 52 |

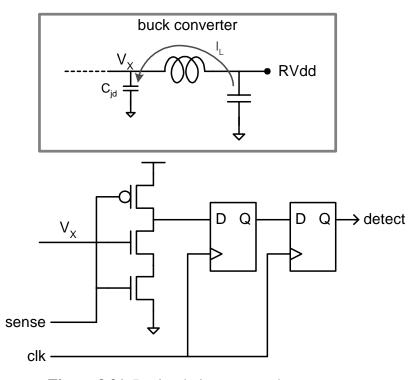

| Figure 3.21. | Recirculating current detector                                     | 54 |

| Figure 4.1.  | Link components                                                    | 58 |

| Figure 4.2.  | Source synchronous parallel interface                              | 59 |

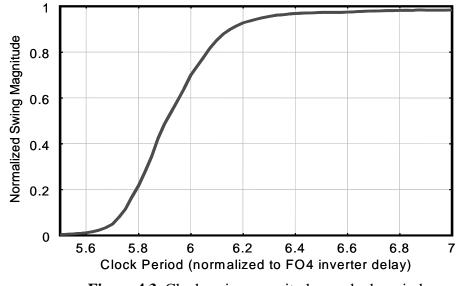

| Figure 4.3.  | Clock swing magnitude vs. clock period                             | 61 |

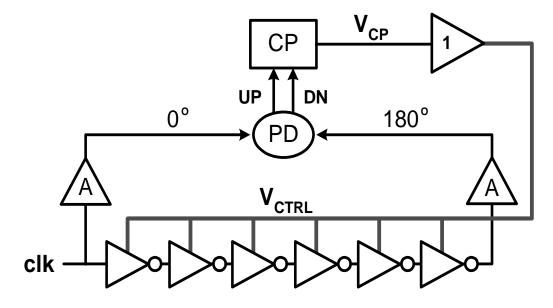

| Figure 4.4.  | Delay-locked loop block diagram                                    | 64 |

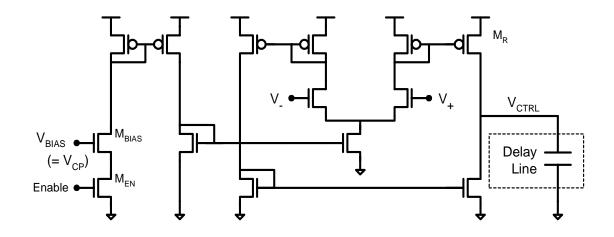

| Figure 4.5.  | Regulating amplifier loaded with delay-line                        | 65 |

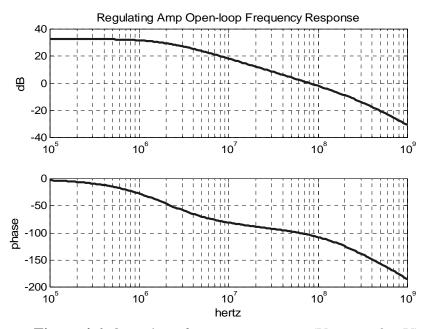

| Figure 4.6.  | Open-loop frequency response ( $V_{CTRL} = 2.6$ -V)                | 66 |

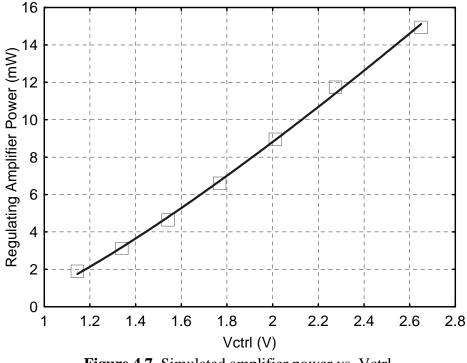

| Figure 4.7.  | Simulated amplifier power vs. Vctrl                                | 67 |

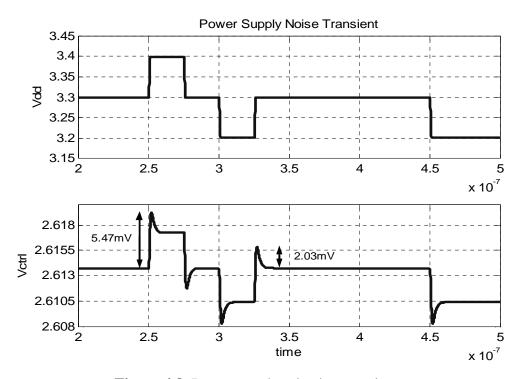

| Figure 4.8.  | Power supply rejection transient response                          | 68 |

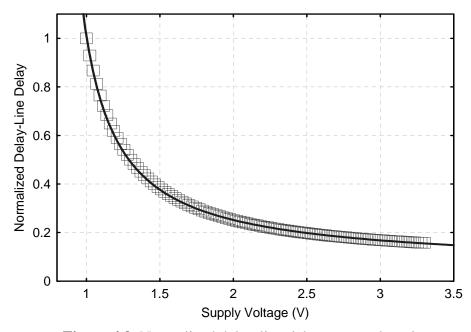

| Figure 4.9.  | Normalized delay-line delay vs. supply voltage                     | 70 |

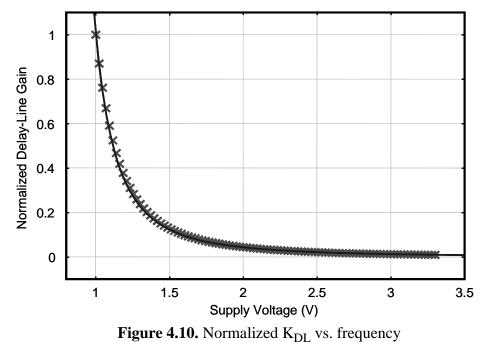

| Figure 4.10. | Normalized K <sub>DL</sub> vs. frequency                           | 71 |

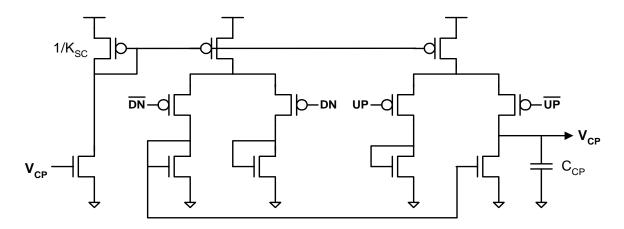

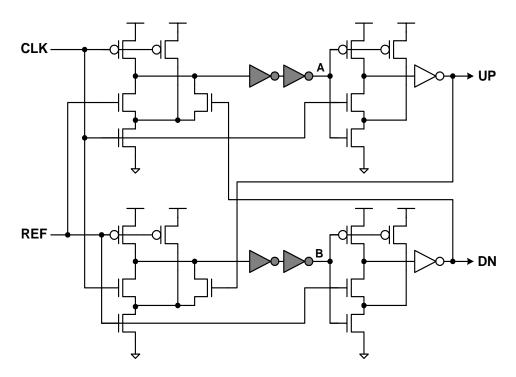

| Figure 4.11. | Differential charge pump                                           | 72 |

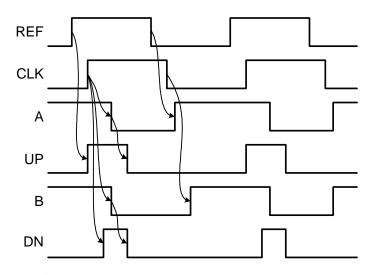

| Figure 4.12. | Phase-only detector                                                | 74 |

| Figure 4.13. | Phase detector transient waveforms                                 | 75 |

| Figure 4.14. | Low-to-high swing converter                                        | 76 |

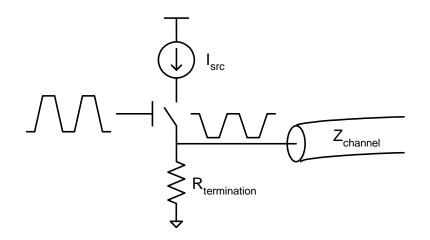

| Figure 4.15. | Ideal high-impedance driver                                        | 78 |

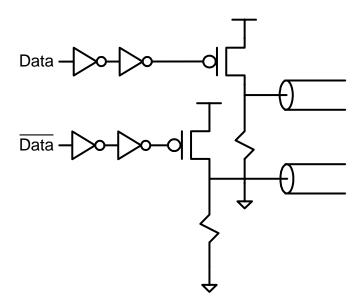

| Figure 4.16. | Single-ended transmitter                                           | 79 |

| Figure 4.17. | Differential signaling                                             | 81 |

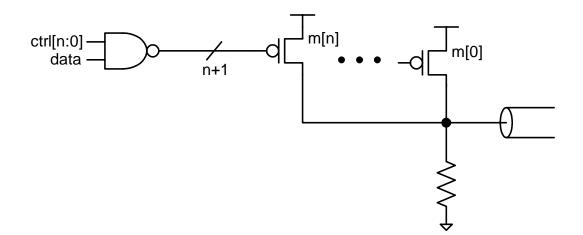

| Figure 4.18. | transmitter output swing control                                   | 82 |

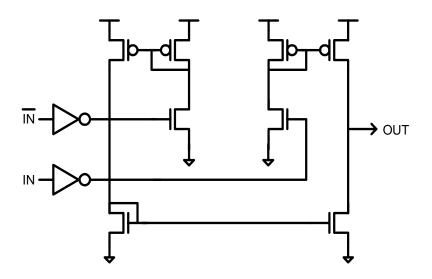

| Figure 4.19. | Transmitter predriver                                              | 84 |

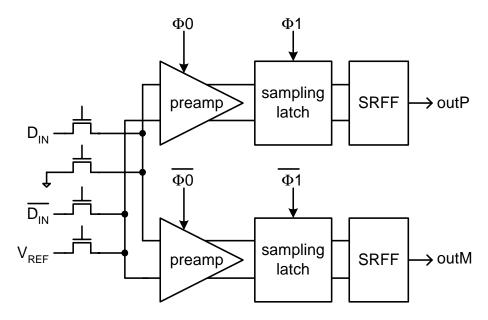

| Figure 4.20. | Receiver block diagram                                             | 85 |

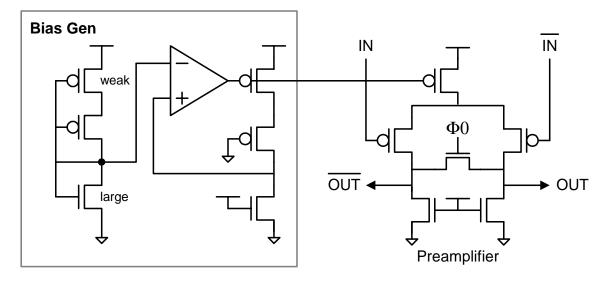

| Figure 4.21. | Preamplifier schematic                                             | 86 |

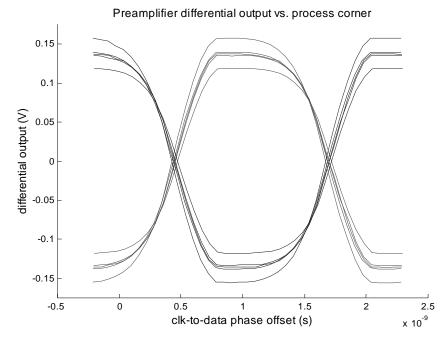

| Figure 4.22. | Preamplifier differential output versus process corner             | 87 |

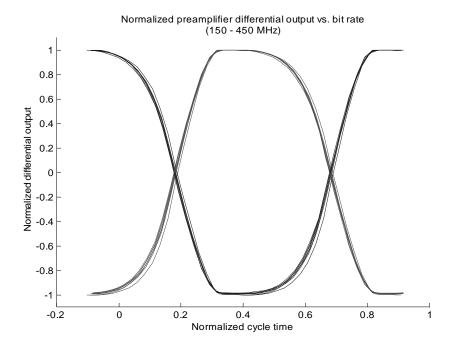

| Figure 4.23. | Preamplifier differential output versus bit rate                   | 88 |

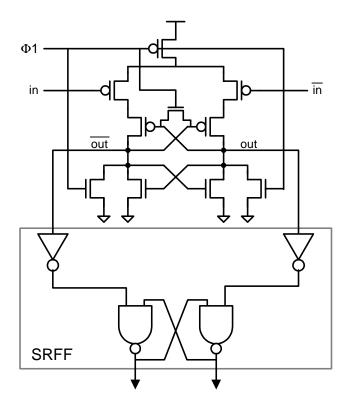

| Figure 4.24. | Regenerative latch and SRFF                                        | 89 |

| Figure 4.25. | Receiver timing                                       | 90  |

|--------------|-------------------------------------------------------|-----|

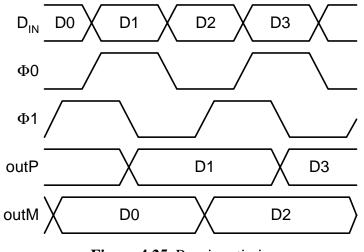

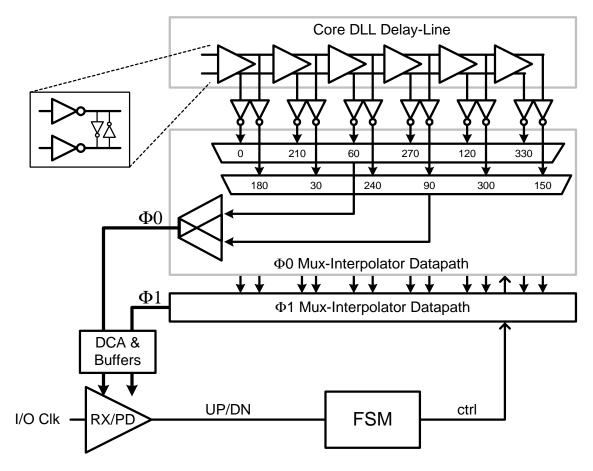

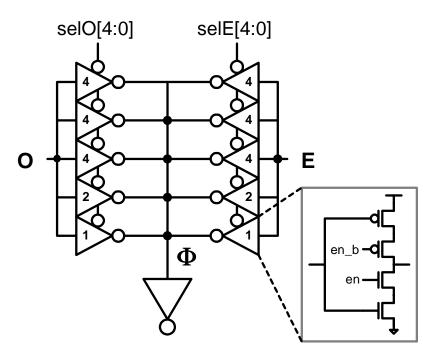

| Figure 4.26. | Digital peripheral loop                               |     |

| Figure 4.27. | Phase interpolation                                   | 95  |

| Figure 4.28. | Digital interpolator                                  | 95  |

| Figure 4.29. | Measured interpolation histogram                      | 96  |

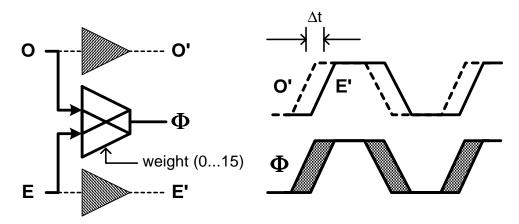

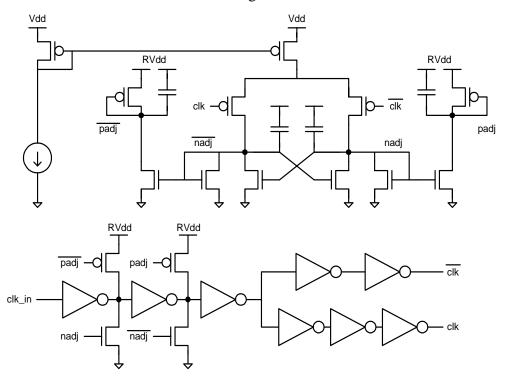

| Figure 4.30. | Duty-cycle adjuster schematic                         | 97  |

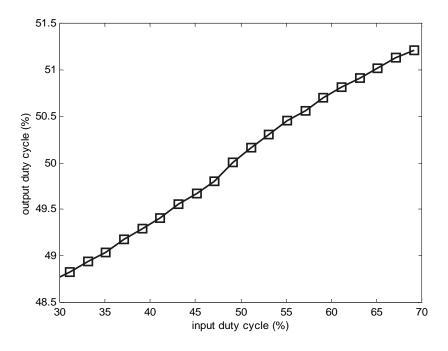

| Figure 4.31. | Duty-cycle adjustment                                 |     |

| Figure 4.32. | Test-chip micrograph                                  | 101 |

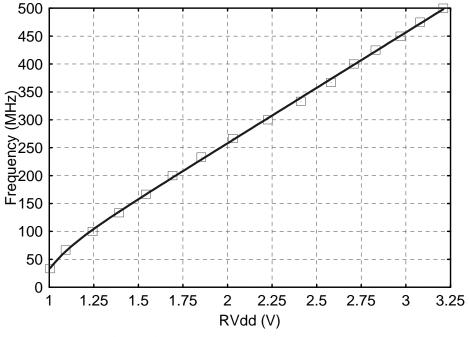

| Figure 4.33. | Regulated voltage vs. frequency                       |     |

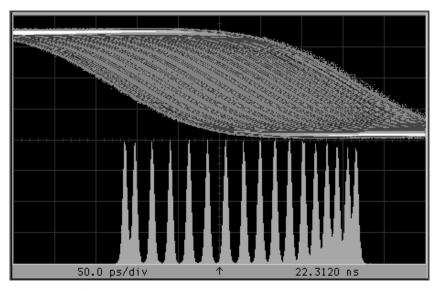

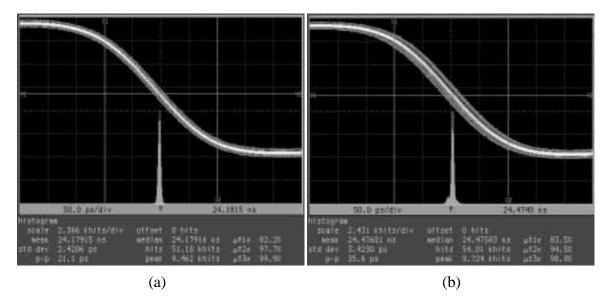

| Figure 4.34. | DLL jitter histogram (a) core, (b) dual               |     |

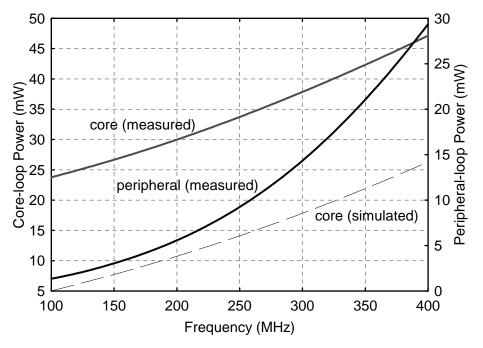

| Figure 4.35. | Dual-loop DLL power consumption vs. frequency         | 104 |

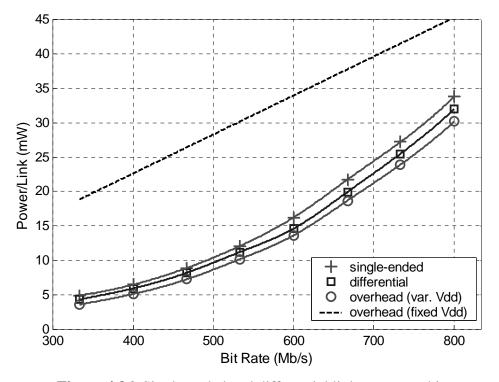

| Figure 4.36. | Single-ended and differential link power vs. bit rate | 106 |

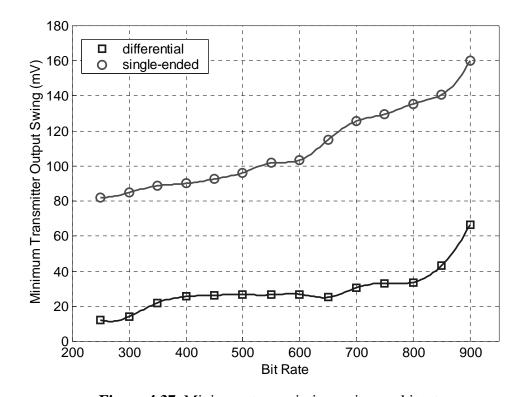

| Figure 4.37. | Minimum transmission swing vs. bit rate               |     |

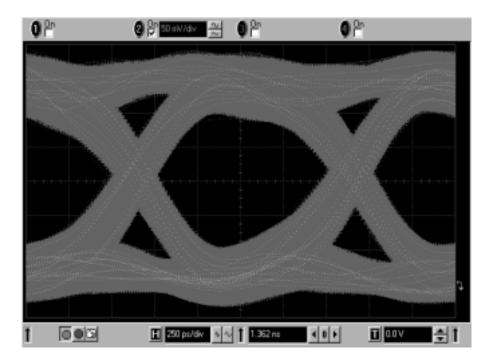

| Figure 4.38. | Transmitted eye at 0.8-Gb/s                           |     |

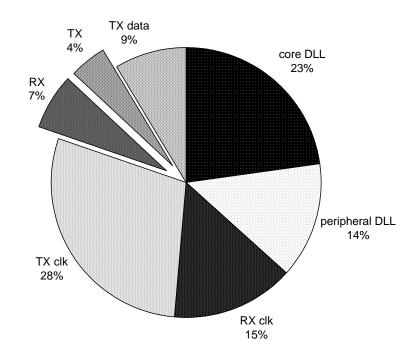

| Figure 4.39. | Power breakdown at 800Mb/s                            | 109 |

|              |                                                       |     |

# **List of Tables**

| Table 4.1. | Dual-loop DLL performance summary         | . 104 |

|------------|-------------------------------------------|-------|

| Table 4.2. | Transmitter output slew-rate vs. bit rate | . 108 |

| Table 5.1  | I/O test chip performance summary         | . 113 |

# **Chapter 1**

## Introduction

Aggressive CMOS technology scaling has enabled explosive growth in the integrated circuits (IC) industry with cheaper and higher performance chips. However, these advancements have led to some chips being limited by the chip-to-chip data communication bandwidth. This limitation has motivated research in the area of high-speed links that interconnect chips [21],[37],[47],[52] and has enabled a significant increase in achievable communication bandwidths. Enabling higher I/O speed and more I/O channels further improves bandwidth, but these approaches also increase power consumption that eats into the overall power budget of the chip. In addition, complexity and area become major design constraints when trying to integrate hundreds of links on a single chip. Therefore, there is a need for building high performance I/O interfaces with low power consumption and low design complexity. This thesis explores using a technique that dynamically scales the supply voltage, called adaptive power supply regulation, to achieve these goals. Controlling the on-chip supply voltage so that the delay of an inverter is a fixed fraction of a bit time allows one to replace precision analog circuits with digital CMOS gates and reduce overall power consumption at the same time.

#### **1.1 Low-Power Techniques**

Performance of digital systems has been increasing exponentially, driven by higher clock frequencies and higher chip complexity. Unfortunately, power in digital systems has also increased as a result and has become a primary concern. Modern high-performance microprocessors can consume more than 100 W [17],[21] and require special cooling and power supply systems. The recent proliferation of portable devices also emphasizes the

need for lowering power dissipation, requiring chips with lower energy consumption to extend battery life.

Power in synchronous CMOS digital systems is dominated by their dynamic power dissipation, which is governed by the following equation:

$$P_{dynamic} = \alpha \ C_{sw} \ V_{DD} \ V_{swing} \ f_{clk,} \tag{1-1}$$

where  $\alpha$  is the switching activity,  $C_{sw}$  is the total switched capacitance,  $V_{DD}$  is the supply voltage,  $V_{swing}$  is the internal swing magnitude of signals (usually equals Vdd for most CMOS gates), and  $f_{clk}$  is the frequency of operation. And since power is the rate of change of energy,

$$E = \alpha C_{sw} V_{DD} V_{swing}. \tag{1-2}$$

Technology scaling enables lower power and energy since when a chip transitions to a new scaled technology, both capacitance and voltage decrease for this chip. Scaling technology also means that the gates get faster, so it is possible to run this scaled chip at higher frequencies, while still dissipating less power than before.

Aside from technology scaling, reducing just the supply voltage for a given technology enables significant reduction in power and energy; both are proportional to the supply voltage squared. However, voltage reduction comes at the expense of slower gate speeds. So, there is a trade-off between performance and energy consumption. Recognizing this relationship between supply voltage and circuit performance, dynamically adjusting the supply voltage to the minimum needed to operate at a given frequency enables one to reduce the energy consumption down the minimum required. This technique is referred to as adaptive power supply regulation, and requires a mechanism that tracks the worst case delay path through the digital circuitry with respect to process, temperature and voltage in order to determine the minimum supply voltage required for proper operation.

There have been several examples of this power saving technique applied to general purpose microprocessors [4],[29],[38],[46] and digital signal processing (DSP) chips

[5],[15],[35] for mobile and other applications where minimizing energy consumption is a priority. These systems commonly rely on the bursty nature of their operation to dynamically adjust the speed and supply voltage in order to minimize the energy consumed for the required computational tasks at hand. Furthermore, these systems employ both hardware and software based schemes to monitor the computational needs of the system.

Adaptive power supply regulation can be used for more than optimizing energy consumption based on the varying computational needs of a digital chip in time. It can also be used for varying computational needs of different parts within a chip. An extreme example of this would be to partition large, somewhat autonomous blocks within a digital chip and operate them at their own optimum frequency and voltage. However, the overhead associated with communication between the potentially asynchronous blocks and to efficiently provide separate voltages to each of them is a formidable challenge. A subset of this example would be to identify a block within a digital chip that consumes a significant component of the overall power and could operate at a lower supply voltage. In other words, a block whose critical delay paths are much shorter than the rest of the digital chip such that, as a separate entity, it could operate at a much lower voltage for the same clock rate. We will see throughout this thesis that a high-speed parallel interface for high-bandwidth communication between chips meets these criterion and its function is briefly introduced next.

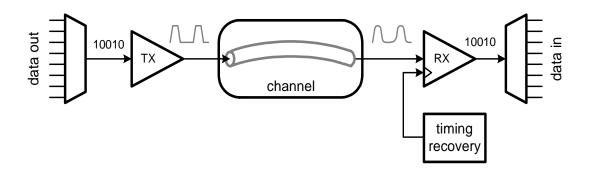

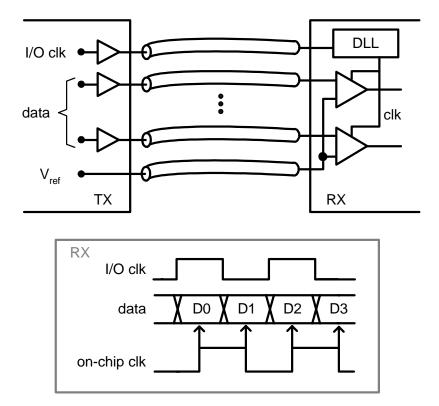

#### **1.2 CMOS Parallel Links**

High-speed links can provide high communication bandwidth between chips and consist of four main components as shown in Figure 1.1. A transmitter converts digital binary data into electrical signals that travel through the channel. This channel is normally modeled as a transmission line and can consist of traces on a printed circuit board (PCB), coaxial cables, shielded or un-shielded twisted pair wires, traces within chip packages, and the connectors that join these various parts together. A receiver then converts the incoming signal back to digital data and requires a timing recovery block to compensate for delay through the channel. A common architecture to enable high bandwidth communication between two chips integrates several parallel sets of these links for data and relies on a separate synchronous clock link for accurate timing recovery [41],[53]. This architecture assumes that delays through the different parallel channels match well. To reduce the power consumed in this link, this thesis focuses on low power link operation and introduces techniques to minimize power in all of the link's components and to enable minimum signal swings through the channel. Although the line power can be significant, power in the supporting circuitry can dominate the total link power when low signal swing levels are used. A significant fraction of the total link power is consumed by the digital circuitry that prepares signals for transmission and the synchronization circuitry that realigns the received data to the system clock of the receiver chip. Since these are predominantly digital circuits, adaptively regulating the supply voltage to the I/O subsystem can enable energy efficient operation without sacrificing performance.

This thesis describes the necessary components to build an adaptive power supply regulator and describes a parallel I/O transceiver that leverages a dynamically scaled supply environment for a simple and robust interface design.

## **1.3 Organization**

Since this work relies on a technique that dynamically regulates the supply voltage to reduce energy consumption, Chapter 2 presents background information that starts with a review of power and delay in digital CMOS circuits and their dependence on process, temperature and voltage variations. Adaptive power supply regulation relies on being able to dynamically track circuit performance to supply the minimum voltage required, so the chapter continues by investigating using inverters as a flexible mechanism for modeling

Figure 1.1. Link components

critical path delay. It then reviews the components necessary to build an adaptive power supply regulator by looking at the characteristics of a buck converter that creates a lower regulated voltage, and the resulting feedback control loop architecture. For effective application to digital systems, Chapter 3 describes a digital implementation of an inherently analog power supply control loop.

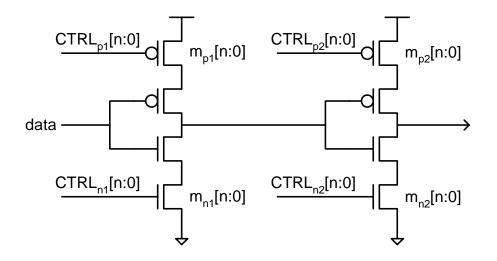

Chapter 4 describes how applying this power saving technique to an I/O subsystem leads to a simple and low-power design. A core DLL, which is a necessary component for timing recovery in the interface, also serves the dual role of determining the "right" voltage of operation with respect to frequency by tracking the worst case delay path in the I/O subsystem. The chapter then describes issues associated with building transceiver circuit components that can function in a variable voltage environment, and presents the resulting transmitter and receiver designs. Another key component of the link is the timing recovery block, which can also leverage the adaptively regulated voltage environment to yield a simpler, mostly digital implementation. The circuit implementations of the building blocks are described and experimentally measured results from a fabricated test-chip prototype present the power savings offered by adaptively regulating the supply voltage that drives the I/O subsystem.

# Chapter 2

## Background

This work focuses on a power-saving technique for digital CMOS circuits that dynamically lowers the supply voltage down to the minimum required for proper operation. By tracking the variable process and environmental effects on circuits, the supply voltage can be regulated to operate circuits at their most energy efficient point without special circuit techniques or logic families, and can be applied to standard static CMOS logic gates. The ability to determine the minimum voltage required for operation requires two components: (i) a mechanism to track circuit performance (or delay) with respect to process, temperature and voltage, and (ii) an efficient power supply regulator to power the digital CMOS circuits. These two issues are the main topics for this chapter.

While simply adjusting the supply voltage to preset levels relative to discrete clock frequencies, set by system performance requirements, enables power reduction, we must also consider the inefficiencies due to overhead voltage margins that are normally imposed on digital circuits. Therefore, before looking at delay tracking mechanisms, Section 2.1 first looks at how process and operating parameters affect circuit performance and power dissipation in digital circuits. Although circuit delay is roughly inversely proportional to supply voltage, process variations and environmental conditions affect device parameters to cause delay and performance variations. By using a unit inverter as being representative of general digital CMOS circuits, we can investigate the energy savings offered with an adaptive power supply regulation scheme that is aware of local process and operating conditions. The assumption that inverters can be used to model the performance of general circuits requires the delay of complex gates track the delay of an inverter across a variety of parameters that affect performance. Section 2.2 investigates the

delay tracking ability of inverters with respect to process, temperature, and voltage variations, and identifies some caveats of simply using inverters as a delay tracking mechanism. An efficient switching power supply regulator design that can enable this power savings is the subject of the rest of this chapter.

### 2.1 Power and Delay in Digital CMOS Circuits

The delay of digital CMOS circuits depends on three main parameters: (*i*) process, (*ii*) temperature, and (*iii*) supply voltage. Variability in manufacturing results in chips that exhibit a range of performance due to variations in device thresholds, oxide thicknesses, doping profiles, etc. Operating conditions also affect performance. Temperature affects the mobility of holes and electrons, and also the transistor's threshold voltage. Lastly, circuit delay strongly depends on supply voltage. The delay of a static CMOS gate can be approximated by the following equation:

$$_{delay} \propto \frac{C_{load} V_{swing}}{\beta (V dd \oplus V_{TH})^{\alpha}}$$

(2-1)

where  $C_{load}$  is the load it drives,  $V_{swing}$  is the swing magnitude of the output (which is Vdd for static CMOS gates), Vdd is the supply voltage, and  $\beta(Vdd-V_{TH})^{\alpha}$  models the device current [39]. For low fields,  $\alpha$  is around 2, but for modern devices  $\alpha$  is as low as 1.25 [20]. Delay variation of a typical fanout-of-4 (FO4) inverter<sup>1</sup> versus supply voltage in an HP0.35µm CMOS process is shown in Figure 2.2 and matches extremely well with the above delay equation for  $\alpha$ =1.4. Assuming that the critical path delay of a digital system is a function of some number of inverter delays<sup>2</sup>, the normalized frequency of operation versus supply voltage can be found by inverting and normalizing the inverter's delay and is also presented in Figure 2.2. The frequency of operation achievable by a chip is roughly

<sup>&</sup>lt;sup>1</sup> A fanout-of-4 inverter is an inverter that driver another inverter with four times its own input capacitance.

<sup>&</sup>lt;sup>2</sup> Section 2.2 shows that a string of inverters can be used to model the critical path delay of digital circuits, consisting of a variety of complex gates, and it tracks well over a wide range of process corners and temperatures. Although the delay of complex gates do not track as well over a wide range of voltage, Section 4.1.1 shows that a string of inverters is a good model for the I/O subsystem's critical path.

**Figure 2.2.** Normalized delay and frequency vs. supply voltage linear with supply voltage. This way of visualizing relative circuit performance versus supply voltage is used extensively throughout this section to analyze the effects of different parameters on performance and power.

To understand what this relationship means for power, the delay data is applied to the dynamic power equation (Equation 2-1) and the resulting normalized power is plotted relative to normalized frequency for two supply voltage configurations in Figure 2.3.

Figure 2.3. Normalized power vs. normalized frequency

Figure 2.4. Normalized energy vs. normalized frequency

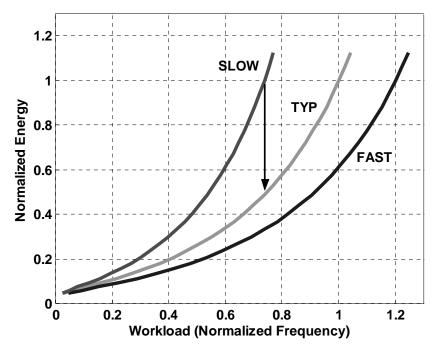

Given a fixed supply voltage, power consumption is proportional to frequency, resulting in a straight line in this figure. Since gate delay can increase if the required operating frequency is reduced, the circuit can operate at lower supply voltages. Therefore, further power savings are possible by reducing the supply voltage to the value indicated by Figure 2.2, for each lower operating frequency. Now, power consumption reduces dramatically for lower frequencies and is proportional to frequency cubed. Another way to analyze this savings is to look at the energy consumed per operation, where an operation is assumed to complete within some fixed number of clock cycles [3]. Figure 2.4 plots the normalized energy consumption per operation versus normalized frequency, again for two voltage conditions. Since the energy consumed is independent of frequency, it is constant regardless of frequency for a fixed supply voltage. However, by appropriately adjusting the supply voltage, there is a quadratic relationship between energy and frequency. Therefore, significant energy savings is possible by operating the chip at lower than peak frequencies.

In addition to the energy savings possible by adaptively regulating the power supply down to lower levels for lower frequencies, there is a potential for saving energy due to inefficiencies found in conventional digital designs that operate off a fixed supply voltage. Variability in circuit performance due to process and temperature variations require

Figure 2.5. Normalized frequency vs. supply voltage vs. corners

conventional designs incorporate overhead voltage margins to guarantee proper operation under worst-case conditions. This is due to the circuit delay's strong dependence on process parameters and temperature as shown by the equations for device transconductance,  $\beta$ , and threshold voltage,  $V_{TH}$ , below. [33]

$$\beta = \mu_{n,p} C_{ox} \frac{W}{L}$$

(2-2)

$$TH = V_{T0} + \gamma(\sqrt{|\mathbb{D} 2\phi_F \mathbb{D} V_{SB}|} \mathbb{D} \sqrt{|2\phi_F|})$$

(2-3)

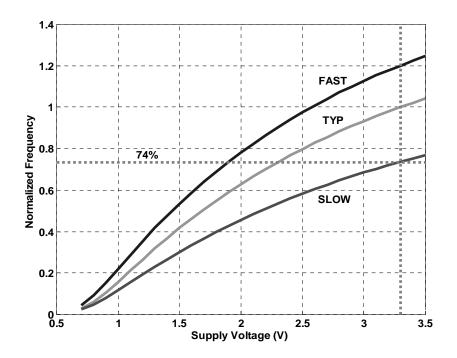

Device transconductance strongly depends on oxide thickness,  $C_{ox}$ , which can vary by 12-% between process runs<sup>1</sup>. Mobility and threshold voltage both have strong dependence on temperature which can significantly degrade circuit speed. Performance dependence on process and temperature can be exemplified by plotting the normalized frequency vs. supply voltage under typical (typical nMOS, typical pMOS, 25-C), fast (fast nMOS, fast pMOS, 0-C), and slow (slow nMOS, slow pMOS, 100-C) corners, shown in Figure 2.5.

<sup>&</sup>lt;sup>1</sup>Oxide thickness variation based on COX parameters for corner case BSIM models for HP0.35µm process.

Although a chip may be able to operate at a peak normalized frequency of 1, under typical conditions and 3.3-V, slow device corners and high temperature degrade circuit performance so that it is unable to function properly at the high target speed. To accommodate this performance variation, chips are normally run at frequencies lower than the normalized peak, identified in the figure at 74-% as an example. Although a slow corner chip can now properly function at this lower frequency, typical and fast corner chips incur large voltage overheads, with a supply fixed at 3.3-V, of 1-V and 1.4-V respectively. This overhead translates into excess power dissipated to allow margins for worst case corners. By taking a look at the energy consumed per operation versus frequency again, as shown in Figure 2.6, since chips under typical and process and temperature conditions can operate at higher speeds with a lower supply voltage and due to energy's quadratic dependence on voltage, not only is energy conserved compared to the fixed supply case, but significant savings is possible at typ and fast corners compared to the slow corner.

A common technique employed by the IC industry to deal with process variability is called speed binning and is common practice for commodity parts such as semiconductor memories and microprocessors. Fabricated chips are categorized into different groups

Figure 2.6. Normalized energy vs. normalized frequency vs. corners

Figure 2.7. Normalized frequency vs. supply voltage vs. temperature

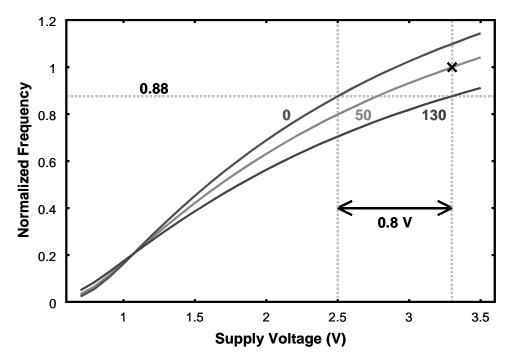

based on the maximum speeds that can be achieved. Although binning allows manufacturers to deal with process variability, operating temperature generally cannot be known *a priori* and therefore chips still need margins to be meet specifications over a wide range of temperatures. Figure 2.7 reveals that chip performance strongly depends on temperature and in order to guarantee operation at the worst case temperature, presented as 130-C, specification at lower speed is inevitable and a potentially large voltage overhead again results for a fixed supply voltage. By actively tracking on-die environmental conditions, namely temperature, dynamic supply voltage regulation accommodates the differences imposed by temperature variations to minimize energy consumption. Furthermore, since temperatures can vary over time, active compensation is necessary to eliminate this time-varying effect on performance, and is not possible with one-time binning after fabrication.

This analysis of how an inverter's speed and power consumption changes relative to process and operating conditions shows there is a potential for considerable power savings due to a large voltage overhead incurred with a fixed supply voltage. While much of the overhead may be reduced, the actual savings that can be achieved depends on how well the critical path's delay tracks relative to an inverter's delay (or the delay of circuit that models the critical path) versus process, voltage, and temperature (PVT). Mismatches between the two lead to margins required to guarantee proper circuit operation. Therefore, the next section investigates how well the delay of several complex gates track the delay of an inverter across PVT.

## 2.2 Delay Tracking

The ability to actively track the performance of digital circuits with respect to local process and temperature variations enables the circuits to operate at a more energy efficient point. Since the performance of a digital system is limited by its worst case critical path delay, an exact replica of this delay path is one of the most accurate ways to measure delay variation with respect to different process corners and variations in operating conditions within a single chip. However, in real designs, designers normally balance delay paths within digital blocks as much as possible. Therefore, identifying a single path to replicate may be difficult. Furthermore, critical paths may differ depending on process corner and operating environment. Instead, we will consider using a series chain of inverters to model the critical path delay. This approach relies on a basic assumption that the delay of complex gates that make-up the critical path track the delay of an inverter. Section 2.2.1 investigates how well the delay of several static and dynamic gates track an inverter's delay. Mismatches measured across voltage variations set the margins necessary for an adaptively supply regulation scheme that use inverters to model the critical path. In addition to matching pure gate delays, the ability to track the delay of wires is also important in modern VLSI systems. Section 2.2.2 this and other non-ideal effects on inverter delay tracking.

#### 2.2.1 Inverter-based tracking

A static CMOS inverter is the simplest unit logic gate and can account for a significant portion of the total gate count in digital IC's. It is the primary gate used for clock distribution and the most efficient mechanism for ramping up drive strength to drive large capacitive loads. Chapter 1 mentioned that an inverter's delay variation versus process,

Figure 2.8. Normalized delay tracking of various complex static and dynamic gate vs. process corner

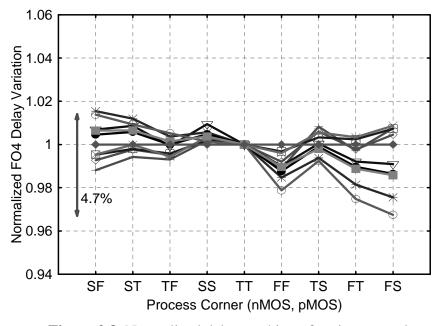

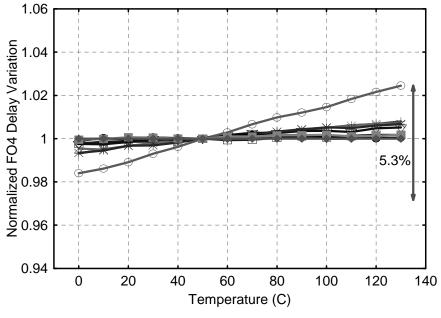

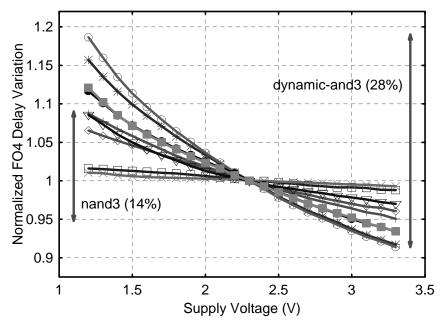

temperature and voltage can be used to predict general circuit performance trends. In this subsection, we look at how valid that assumption is by measuring the delay of various static and dynamic complex gates (nand2, nand3, nor2, nor3, transmission gate, dynamic-nand2, -nand3, -nor2, and -nor3) relative to an inverter delay, across a wide range of process corners, temperatures and voltages. Results are presented in terms of its tracking variation with respect to the variable on the x-axis, by taking the normalized delay of the gates with respect to a FO4 inverter and then calculating how much it varies relative to a fixed point on the x-axis value. Delay tracking variations versus process corner are presented first, in Figure 2.8, where FS denotes the fast nMOS, slow pMOS process corner. The lines are all relatively flat which is an indication that delay of these gates track well with the delay of an inverter across different process corners. The same holds true for tracking with respect to temperature as shown in Figure 2.9, where temperature ranges from 0-C to 130-C. Unfortunately, tracking is not as good across a wide range of supply voltages, presented in Figure 2.10. Variations in normalized delay can be attributed to velocity saturation which affects short-channel devices more than longer-channel devices. If we take a NAND3 for example, there is a series stack of three nMOS devices which must all be conducting to pull the output low. This stack of three

Figure 2.9. Normalized delay tracking of various complex static and dynamic gates vs. temperature

minimum channel length devices can be modeled as a single device with an effective channel length that is three times longer. An inverter, on the other hand, consists of a single minimum channel length nMOS device. Higher lateral electrical fields saturate the velocity of carriers in shorter channels lengths more than in longer channels. This

Figure 2.10. Delay tracking of various static and complex gates normalized to  $L_{min}$  FO4 inverter vs. supply voltage

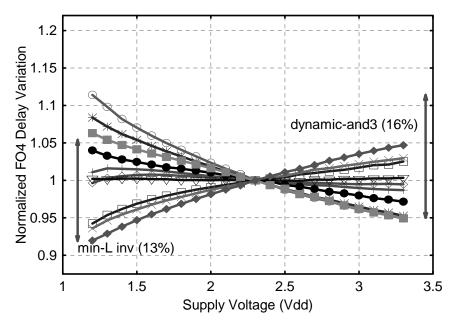

**Figure 2.11.** Delay tracking of various static and complex gates normalized to 1.5\*L<sub>min</sub> FO4 inverter vs. supply voltage

saturation makes the current in an inverter less sensitive to Vdd, and thus the delay of a NAND3 increases faster than an inverter as the supply voltage decreases. As a result, the lines slope downward as supply voltage increases to varying degrees depending on the gate. The worst case critical path delay occurs at the lowest supply voltage. This unfortunately means that the extra voltage margins required for lower voltages leads to excess power consumption at higher speeds and voltages when the chip consumes more power.

One way to mitigate this velocity saturation effect is to change the reference circuit to instead use inverters with longer channel lengths. Figure 2.11 reveals that worst case variation is reduced from 28-% to 17-%, when using an inverter with lengths 1.5 times the minimum channel length as the reference. However, notice that now several curves slope upward where the steepest is for a minimum channel length inverter. This mix of upward and downward delay tracking trends relative to supply voltage makes finding the worst case conditions for the critical path challenging since it varies with the types of gates used.

Depending on the gates that constitute the critical path, the choice of channel length for inverters in the delay-line varies. Furthermore, delay margins must be added to guarantee operation across all voltage conditions. As an example, let us choose 2.3-V to be the nominal voltage condition for design and we have a choice between two channel lengths:  $L_{min}$  and  $1.5*L_{min}$ . If the critical path consists mostly of dynamic-and3 gates, extra delay margin is necessary to guarantee proper operation under low frequency and low supply conditions. But utilizing longer channel length inverters to model its delay reduces the margin from 18-% to 12-%. On the other hand, if the critical path consists mostly of minimum channel length inverters, using 1.5\*Lmin inverters to model its critical path requires an additional 5-% delay margin to guarantee operation under high speed and voltage conditions. Instead, using minimum channel length inverters in the delay line would be best. In fact, matching the delay-line elements with the gates that dominate the critical path would yield the best matching. Chapter 4 shows that an inverter chain is a good match for an I/O subsystem because the worst case delay path is in the clock distribution network which predominantly consists of inverters.

#### 2.2.2 Other non-ideal effects

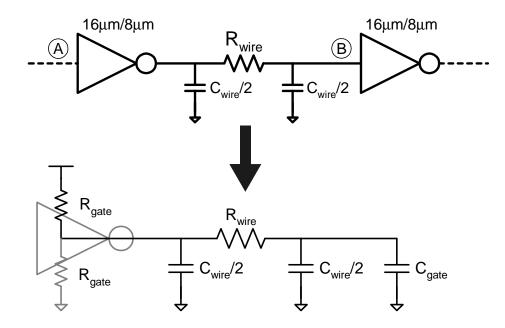

In addition to gate delays, critical paths consist of wires that interconnect different gates and functional blocks together. The delay through these wires are not governed by the same physical principles as in MOS gates. Therefore, it is important to consider how tracking varies when appreciable wire loading is present. In large digital systems, the delay associated with driving long busses across a chip can be large and often require repeater buffers to cut down the quadratic dependence on length to a linear one [1],[16]. This analysis utilizes a simple test-bench circuit consisting of inverters interconnected with a distributed  $\pi$ -model for a wire of variable lengths, as shown in Figure 2.12. Relatively large device sizes and wire lengths are used in order for wire resistance to be non-negligible. By modeling the inverter with an output resistance ( $R_{gate}$ ), this test bench reduces to a simple RC model for delay given by the following equation:

$$T_{delay} = R_{gate} \cdot (C_{gate} + C_{wire}) + R_{wire} \cdot \left(C_{gate} + \frac{C_{wire}}{2}\right).$$

(2-4)

The simulated delays of an inverter with wires (of different lengths ranging from 500- $\mu$ m to 3000- $\mu$ m and 1- $\mu$ m wide) normalized to an inverter delay without wires, but with the

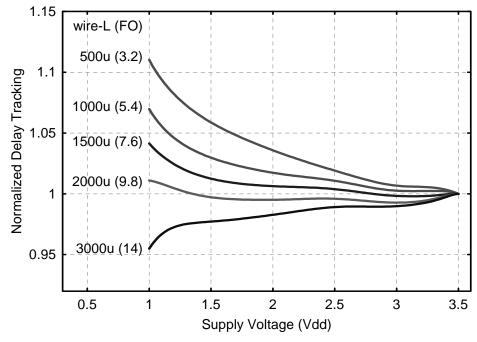

Figure 2.13. Wire delay tracking vs. supply voltage

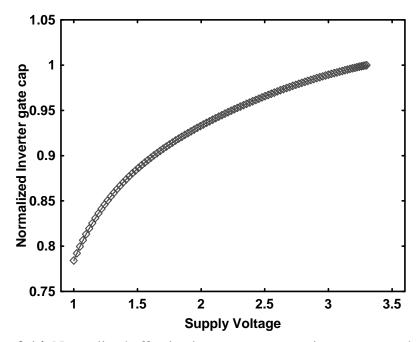

same effective fanout at 3.3-V, versus supply voltage are presented in Figure 2.13. Wire lengths and effective fanouts with the wire loading are labeled on the graph. Across this wide range of lengths, delay tracking varies less than 12-% across a wide supply voltage range. As supply voltage decreases, inverter drive strength reduces and  $R_{gate}$  increases. As

Figure 2.12. Wire delay test bench and RC model

Figure 2.14. Normalized effective inverter gate capacitance vs. supply voltage

a result, one would expect the contribution of wire delay to become less significant and result in an upward slope in the delay vs. voltage plot. However, the opposite is observed for wire lengths less than 2000-µm. This can be attributed to a reduction in the effective gate capacitance on inverters as supply voltage decreases, as shown in Figure 2.14. Once the load is almost entirely dominated by the wire, the expected upward trend is observed, which is for wire lengths greater than 2000-µm in this example. In the case of long wires that use repeaters to linearize delay with respect to distance (versus a quadratic relationship for non-repeated wires), since optimal fanout is on the order of 4, additional delay margins of up to 8-% will be necessary to meet the worst-case delay conditions occurring at low supply voltages.

Apart from variations due to velocity saturation effects and wires, the inverter model of the critical path must also consider other non-ideal effects that can adversely affect tracking. Although a chain of inverters may be able to model how different process and environmental conditions generally affect individual chips, intra-die variations can lead to delay mismatches which are more difficult to track. For example, hot spots in a chip can arise from differing circuit activity in different parts of the chip to cause temperature gradients within in chip. Since the silicon substrate is an imperfect thermal conductor, if the delay tracking inverter-chain model is located far from the critical path that happens to be in or near the hot spot, the model may be incorrectly optimistic. Higher activity also means larger currents and so larger resulting IR drops on the supply lines may exacerbate the mismatch. Intra-die process variations are generally less than the variations between individual chips, but it can also cause delay mismatches. All of these non-ideal effects stress the importance of location and strategic placement of the inverter chain that models delay to accurately monitor local conditions. As mentioned before, since the critical path may vary and exist in different parts of the chip during normal operation, multiple inverter chains may be required to monitor the variations within a chip and capture the worst case. However, circuit layout may not allow easy integration of these inverter blocks close to the critical path in the core logic. Therefore, the model may require additional margins to account for these variations. Careful characterization of potential intra-die process, temperature, and current differences can find the minimum margins necessary. An ability to tune the inverter chain model to actively find and set the minimum margin may also prove useful.

#### 2.2.3 Delay Tracking Summary

This section has investigated the potential delay tracking mismatches between an inverter model of the critical path and actual gates and wire that make up delay paths in an actual digital system. Although there is a large potential for optimizing energy consumption by adaptively adjusting the supply voltage to the minimum required to meet timing, additional margins to compensate for tracking mismatches are necessary and reduce some of the energy savings that may be possible in a perfect environment. While the worst case corner for conventional digital circuits are in the slow corner, we have seen that the delay of complex static and dynamic gates can speed up or slow down relative to an inverter delay for different conditions. Tracking is extremely good with respect to process and temperature, but it can vary by 28-% across voltage. Therefore, a designer must adjust the delay elements used in the delay-line with respect to the types of gates in the critical path and use the tracking relationships shown in Figures 2.10-12 to reduce the delay margins needed.

Now that we know how to deal with some of the caveats of designing circuits in a regulated supply voltage environment, we need a power-supply regulator that can dynamically scale the voltage with respect to the desired frequency of operation, process and operating conditions. Issues associated with designing such a regulator is the topic of the next section.

### 2.3 Adaptive power supply regulation

Given a model of the critical path, adaptive power supply regulation needs to generate the minimum supply voltage required for proper operation at the desired frequency and efficiently distribute it to the synchronous digital system. This task requires two components: (i) a power supply regulator and (ii) a control mechanism to generate the correct voltage. Although a linear regulator can be used to supply power as demonstrated in [29], the power that the regulator itself consumes can be substantial and therefore counteracts the power savings of this approach. Instead, a switching regulator that has much higher conversion efficiency is preferred and is described in the following section. Driving the output of this regulator to the desired voltage with respect to operating frequency requires a feedback control loop that utilizes a ring oscillator to measure and monitor circuit performance, and Section 2.3.2 covers this design in more detail.

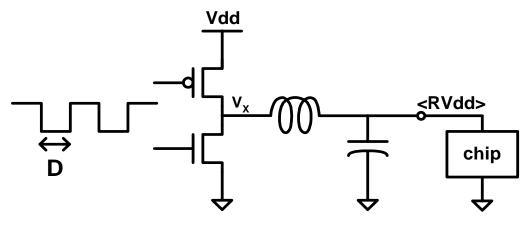

#### 2.3.1 Buck Converter

In order to dynamically generate a lower supply voltage from a fixed high voltage set by the system, a DC-DC step-down converter is used. The buck converter, shown in Figure 2.15, is a switching regulator that can efficiently deliver power to a load. Its operation is straight forward and relies on an inductor and capacitor that act as a low-pass filter. Although there have been significant developments to build inductors and capacitors on-chip [54], current CMOS technology still cannot provide reactive elements that store sufficient energy to efficiently convert power, and therefore this design requires off-chip reactive elements. As long as the switching frequency of the input pulse-width modulated (PWM) rectangular-waves is at least an order of magnitude greater than the cut-off

Figure 2.15. Buck converter

frequency of the low-pass filter, the output voltage of the filter is an average value where its magnitude is set by the duty-cycle of the incoming rectangular-wave. Low pass filtering through the inductor and capacitor therefore reduces the AC component of the incoming rectangular wave to an acceptable ripple and its magnitude is set by the ratio of the switching frequency to the filter cut-off frequency. Since the LC filter is a second-order filter, high-frequency AC attenuation is 40-dB/dec. The pMOS and nMOS transistors are large on-chip devices that chop the input high voltage Vdd to generate a rectangular-wave at node  $V_x$  with an average voltage that is equal to the desired output voltage with the following equation:

$$\langle RVdd \rangle = D \cdot Vdd \tag{2-5}$$

Therefore, modulating the duty-cycle, *D*, of the input rectangular wave modulates the regulated output voltage, *RVdd*. These devices also support the average current delivered to the load.

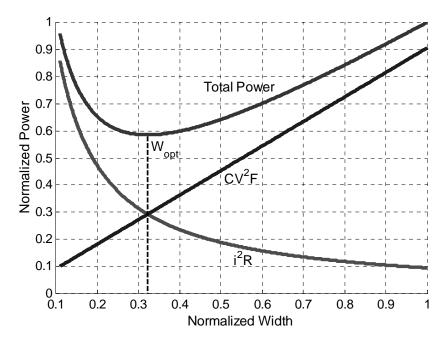

The conversion efficiency of this type of converter approaches 100-% as all its components become ideal. However, due to several loss mechanisms, efficiency degrades, but values greater than 90-% are still attainable [6],[24],[32]. Using off-chip reactive components can provide very high quality reactive elements with quality factors (Q) greater than 100 and are not the dominant source of loss. Instead, loss is dominated by the resistive losses through the on-chip switching transistors and the power required to switch them. The "on" resistance of these devices is inversely proportional to the gate width (W).

The resistive loss, denoted as  $P_{IR}$ , also strongly depends on the current magnitudes that flow through these devices and is set by Equation 2-6. Wider devices clearly yield lower resistive losses. However, the switching power required to drive these devices constrains the size of these devices since its power is governed by Equation 2-7, where C' is the effective capacitance per micron of gate width (including capacitance of the buffer chain that drives it), Vdd is the supply voltage, and  $F_s$  is the frequency at which the converter is switched. Equation 2-8 represents the optimal gate sizing for these devices found by solving for gate width, W, that yields the minimum total power for a given load current,  $i_{ld-rms}$ .

$$_{IR} = \frac{i_{ld}^2 \oplus rms^R ON}{W}$$

(2-6)

$$P_{gate} = C' \cdot W \cdot V dd^2 \cdot F_s \tag{2-7}$$

$$W_{opt} = \sqrt{\frac{i_{ld \, \text{D} \, rms}^2 R_{ON}}{C' V dd^2 F_s}} \tag{2-8}$$

Figure 2.16 illustrates the normalized sum of the losses in the switching transistors versus gate width and load current and reveals an optimum gate width.

In Equation 2-8, notice two variables, load current and switching frequency, also affect the optimal gate size. Therefore, a designer must consider the power consumption specifications of the load to accurately determine the optimum gate width, which is set by the maximum power requirements. However, for performance driven voltage regulation, power consumption dramatically reduces at lower frequencies due to power's quadratic dependence on voltage. Under lower power conditions, the resistive losses also quickly reduce, but gate switching power remains constant for fixed switching transistor sizes. Appropriately adjusting the widths to be closer to optimal sizing under performance driven load conditions therefore reduces the losses associated with the converter. The optimum gate width varies with load current and Section 3.2 describes a technique that

**Figure 2.16.** Buck converter switching transistor power loss vs. width leverages this property to achieve higher conversion efficiencies. Switching frequency also affects optimal sizing, but is a nominally fixed parameter constrained by several other factors. Higher switching frequency allows a higher LC filter cut-off frequency, which requires smaller inductor and capacitor sizes. This is desirable for portable applications where form factor is a primary concern. However, magnetic saturation of the magnetic core, introduced to increase inductance without affecting the series resistive losses, limits the maximum frequency [6].

Given that the switching frequency is at least an order of magnitude higher than the LC cut-off frequency, a frequency-domain transfer function of the buck converter can be approximated by the following equation:

$$H_{LC}(s) = \frac{1/LC}{s^2 + \left(\frac{R_S}{L} + \frac{1}{R_L C}\right)s + \frac{1}{LC}\left(1 + \frac{R_S}{R_L}\right)},$$

(2-9)

where the L and C are the inductor and capacitor values,  $R_S$  is the series "on" resistance of the switching transistors, and  $R_L$  is the resistance of the load chip and dielectric loss of the capacitor at the output. Given the availability of high-quality off-chip inductors and capacitors, there is a resonance at the cut-off frequency due to the complex pole pair of the LC filter. Although high Q's are desirable for efficient power conversion, it can complicate the enclosing control loop design.

Given this mechanism for efficiently delivering power to the load, this adaptive power supply regulation technique needs a way of setting the duty-cycle of the input rectangular wave to regulate the buck converter's output to the desired voltage with respect to some desired frequency of operation. This is the topic of the next subsection.

#### 2.3.2 PID Control Loop

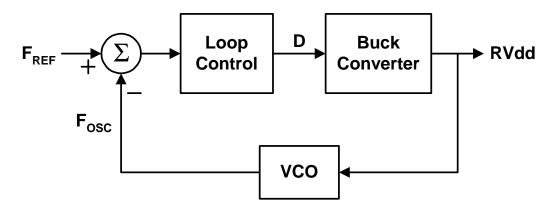

Adaptively setting the duty-cycle of the PWM rectangular to regulate the output voltage with respect to some desired frequency of operation requires a control loop, as shown in Figure 2.17. It consists of a voltage-controlled oscillator (VCO) that converts the regulated voltage output of the buck converter into a clock signal that oscillates at a voltage-dependent frequency,  $F_{OSC}$ . This VCO consists of an odd number of inverters in a ring, which oscillates due to positive feedback, and acts to monitor variations in circuit performance relative to process and operating conditions. Taking the difference between the input reference,  $F_{REF}$ , and  $F_{OSC}$  generates an error that feeds into the loop control block. Through negative feedback, the loop locks the output voltage such that the two frequencies match. Therefore, the output voltage tracks with the input frequency reference, where the relationship between the two is dictated by the performance monitoring VCO.

Figure 2.17. Control-loop block diagram

Figure 2.18. PID control-loop frequency-domain model

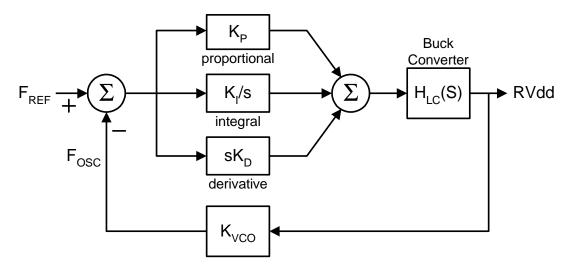

To achieve good transient response characteristics and stability without sacrificing bandwidth, the loop uses proportional, integral, and derivative (PID) control. A frequency-domain model of this PID loop is presented in Figure 2.18. The resulting open-loop transfer function (loop gain) is as follows:

Loop Gain =

$$H_{LC}K_{VCO}\left(K_P + \frac{K_I}{s} + sK_D\right)e^{\text{D}sT}$$

(2-10)

$K_P$ ,  $K_I$ , and  $K_D$  set the pole and zero locations of the proportional, integral, and derivative control block.  $K_{VCO}$  represents the oscillator gain (Hz/V). Due to the time required to perform the PID control calculations, its delay (*T*) through the loop causes additional negative phase shift accounted for by the exponential term in the equation.

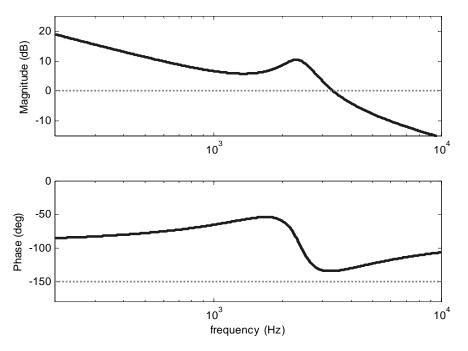

One difficulty associated with designing this type of controller arises from the resonant peak in the frequency response of the buck converter. For simple integral control, which consists of an integrator followed by the buck converter, there is a potential for instability. An open-loop frequency analysis for this type of loop shows that if the magnitude of the resonant peak crosses above the unity-gain magnitude, negative phase shift due the integrator pole and a pair of poles from the LC filter eliminates phase margin. Therefore, the integrator's gain must be sufficiently low as to guarantee that the buck converter's resonant peak never crosses unity gain. Unfortunately, such a configuration

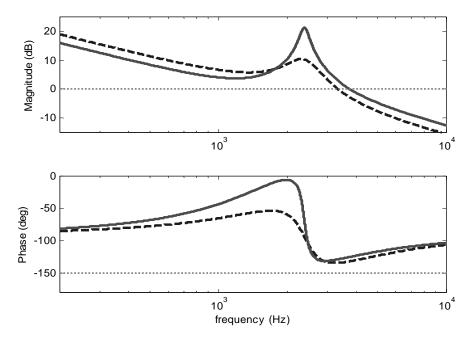

Figure 2.19. PID control open-loop frequency response

leads to low loop bandwidth and slow closed-loop transient response characteristics. To combat this effect, adding a pair of zeros, utilizing proportional and derivative blocks, can stabilize the loop without sacrificing bandwidth. Introducing the zeros at frequencies below the cut-off frequency of the LC filter pushes unity gain crossing of the open-loop response beyond the resonant peak and roles off at -20dB/dec. Furthermore, positive phase shift from the zeros provides sufficient phase margin for a stable loop, as the magnitude and phase response of the simulated open-loop transfer function in Figure 2.19 demonstrates. The bandwidth of the loop extends beyond what was achievable with integral control alone and the resonant peak of the regulator LC is no longer a limiting factor since it occurs below the unity gain frequency. In addition, because the bandwidth exceeds the LC filter's cut-off frequency, the loop can quickly response also prevents other noise sources, such as sudden transients in the supply voltage to the buck converter, from propagating to the output.

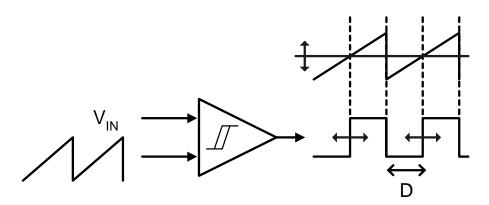

Implementation of the controller in Figure 2.17 relies on the ability to generate a PWM rectangular wave, where the duty-cycle (D) is the value dictated by the output of a PID control block. One possible approach would be to use a frequency detector that compares

Figure 2.20. PWM rectangular wave generation

the incoming reference clock with the output of the oscillator and generate an analog voltage that corresponds to the frequency difference (or error). This error then drives the PID control implemented with a set of amplifiers to generate an analog voltage that corresponds to the desired output voltage. Translating this voltage to the appropriate duty-cycle then relies on a comparator that compares a linear ramp wave that has a period equal to the switching frequency of the buck converter to the PID control output. Figure 2.20 illustrates its operation. While the PID output is less than the ramp input, the output of the comparator is low and goes high once the ramp exceeds the PID output. As a result, changing the PID output proportionally changes the duty-cycle of the rectangular wave. The enclosing feedback loop compensates for any offsets and non-linearities that may exist in the translation.

Although this is a straight forward approach for implementing the PID control, it requires several analog components that can be sensitive to supply and substrates noise that exists in the targeted digital system. Also notice that the update rate of the buck converter is set by its switching frequency. Therefore, the update of the control blocks can occur at a rate much lower than the reference clock frequency. In addition, there is an inherent analog-to-digital (A/D) conversion that occurs in the ring oscillator, which takes an analog input voltage and generates a digital clock signal. Therefore, there is a potential to build this controller consisting entirely of digital gates, and can be embedded along with the rest of the digital system to which power is delivered. The issues and design of a digital control loop are the topics of the next chapter.

#### 2.4 Summary

Power consumption in digital systems has been increasing at an accelerated rate and one of the most effective ways to reduce unnecessary power consumption is to minimize the overhead voltage normally required in fixed voltage designs by dynamically adjusting the voltage to the minimum required for operation at a desired frequency. Given the quadratic dependence on voltage, significant reduction in power consumption is possible and this technique can enable more energy efficient operation for synchronous digital circuits.

The minimum supply voltage required with respect to frequency can be found by using a ring oscillator that models the critical delay path in a synchronous digital system and use negative feedback control to servo the output of an efficient switching regulator [18]. Given the difficulty associated with generating an exact replica of the critical path, a more flexible approach to modeling delay based on inverters is possible. This approach, however, still requires some overhead margins to account for imperfect matching over a wide range of supply voltages stemming from velocity saturation effects. The tracking performance of the power supply regulator is set by the bandwidth of the control loop, which can be improved with a PID control that guarantees stability without sacrificing bandwidth. A PID loop has the added advantage that its bandwidth extends beyond the cut-off frequency of the LC filter so that the loop can quickly respond to noise injected at the output due to load transients. Although there are several approaches to designing this adaptive supply voltage regulator, the following chapter describes a fully digital implementation that fits well within a larger digital system.

# Chapter 3

## **Digital Power-Supply Controller**

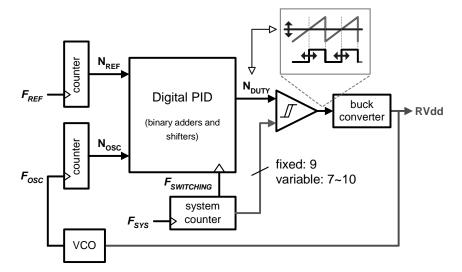

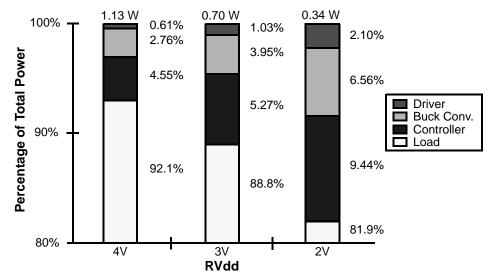

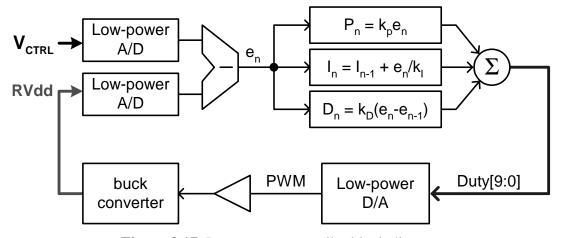

This chapter describes a fully-digital implementation of the analog power supply controller described in Chapter 2, which avoids static currents necessary in analog circuits and sensitivity to digital supply noise when embedded within a larger digital system. Since the power consumed by the controller contributes to the overhead power consumed by the regulator, a controller that consumes very little power or one whose power tracks the power delivered to the load is desirable for enabling high conversion efficiency over a wide range of load power and chip operating frequencies. This is especially true for performance driven adaptive voltage regulation schemes, since power consumption has a cubed dependence on frequency. In this chapter, several techniques are introduced to achieve this goal of reducing controller power whenever possible by building a digital IIR filter to implement the PID control. This requires three main components: (i) A/D conversion, (ii) digital PID control, and (iii) D/A conversion, along with the buck converter, as shown in Figure 3.1.

The chapter starts with a section that describes two techniques for A/D conversion

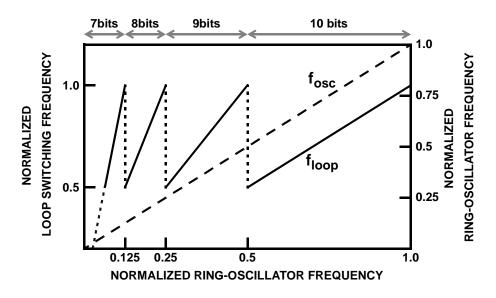

Figure 3.1. Digital controller block diagram

based on the inherent A/D property of a ring oscillator and then presents a discrete-time sampled data implementation of the analog PID control blocks. The chapter continues with a description of a variable-frequency controller which allows the digital controller to operate with adaptive power supply regulation. Then, Section 3.3 presents a simpler and lower power digital controller that operates at a fixed frequency, which has been implemented to drive a low-power parallel link described in Chapter 4. An additional advantage of building a fully-digital controller is the ease with which non-linear techniques can be implemented to improve power conversion efficiency. These techniques are described in Section 3.4.

#### 3.1 A/D Conversion

A digital controller first requires the analog inputs and outputs of the system be converted into digital signals in order to process them with digital functional units. As described in Chapter 2, this adaptive supply-voltage regulation scheme uses the delay of inverters  $(T_{INV})$  to model the critical path in the digital system and monitor how it reacts to process, temperature, and voltage variations. A ring oscillator, consisting of an odd number of inverters in a ring  $(n_{stages})$ , performs a voltage-to-frequency conversion, where the oscillation period is  $2 \cdot n_{stages} \cdot T_{INV}$ , since an edge traverses through the inverters in the ring twice within a period. As illustrated in Figure 3.2, tapping out at a single point in the ring and counting the digital clock signal over a fixed period of time performs a simple A/D conversion. The binary output is a quantized representation of the voltage  $(V_{IN})$  that depends on the counting interval  $(T_{count})$ , with the following equation:

$$N = \frac{T_{count}}{2 \cdot n_{stages} \cdot T_{INV}}.$$

(3-1)

Figure 3.2. Ring oscillator and counter based A/D converter

At the end of each interval, N is stored and the counter resets to zero for the subsequent count.  $F_{count}$  (=  $1/T_{count}$ ) is set by the buck converter's switching frequency. Since N depends on  $T_{count}$  and  $n_{stages}$ , longer counting intervals and less inverter stages enable higher resolution of the output. However, there is a  $n_{stages} \ge 3$  limit and  $T_{count}$  affects the overall loop dynamics. It is important to count over the full period to obtain an average magnitude of the power supply due to a small voltage ripple at the output of the buck converter.

Since the performance of the counter can be measured as a function of inverter delays, as long as its critical path is less than double the number of inverters in the ring, the counter can also operate at the same voltage as the oscillator. In the case of a simple ripple counter, only the first stage, implemented as a toggle flip-flop, sets the critical path since subsequent stages operate at lower rates. Figure 3.3 illustrates the ring oscillator, ripple counter, and finite state machine (FSM) used to implement this simple A/D converter [48]. The finite state machine not only resets the counter, but also allocates additional time at the end of the counting interval, before the latching the output, to accommodate for the worst-case ripple path through the counter. Assuming the clk-to-Q delay of a flip-flop is on the order of 2-3 inverter delays, the worst-case ripple delay is set by the number of bits

Figure 3.3. A/D converter detailed schematic

in the counter  $(n_{bits})$  and the following equation:

Worst-case ripple path =

$$3n_{bits} \cdot T_{INV}$$

. (3-2)

Hence, for the following inequality,

$$\Delta_{delay} = 3n_{bits} \cdot T_{INV} \oplus 2n_{stages} \cdot T_{INV} > 0, \qquad (3-3)$$

the FSM must allow an additional  $\Delta_{delay}$  of time before latching the counter outputs. Since the FSM enables the counter to operate at the same frequency and voltage as the ring oscillator, the A/D converter's power consumption tracks with the ring oscillator and ultimately with the rest of the digital system to which power is supplied.

This simple approach to building an A/D converter can be improved by using phase information to increase digital resolution of the analog voltage without a power penalty. High switching frequency (for the buck converter) and high resolution are desirable for building a digitally controlled regulator with good performance. Higher switching frequencies enable higher bandwidths for the control loop and higher resolution minimizes quantization error that results from a digital implementation of an inherently analog loop. Given a target switching frequency of 1-MHz and 10 bits of resolution, a simple ring oscillator and counter used for A/D conversion must run at an extremely high rate. Since the least significant bit (LSB) corresponds to a single oscillator cycle, to convert the maximum voltage to the maximum digital output of the counter, the counter must run at 1-GHz. This leads to significant power consumption in the A/D conversion block which increases overhead power and degrades the converter efficiency. Instead, reducing the LSB to a fraction of the oscillation period is preferable.

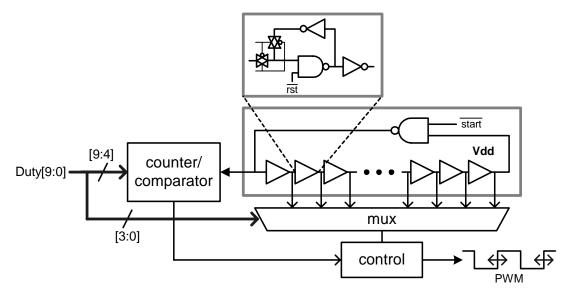

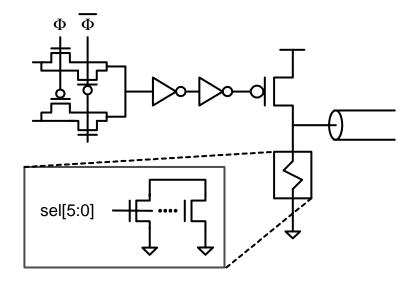

To lower the A/D converter's power consumption, an improved version based on a technique that relies on a delay-line instead of a ring oscillator [8] is presented in Figure 3.4. In this implementation, the ring oscillator and counter structure is retained for hardware reuse and to avoid the geometrically increasing number of delay stages with each additional bit of resolution. The counter output now only accounts for the five higher order bits, N[9:5], of the digital output. Similar to the original approach, the counter counts pulses out of the ring oscillator over the switching period of the buck converter, but

generates a course grain representation of the input voltage. The lower order bits of resolution are extracted from the delay line. Instead of a just implementing a delay line consisting of inverters, each delay element consists of a static pass transistor latch that captures the internal state of the ring at the end of the counting period. A synthesized encoder takes the output of each of the 32 delay stages and determines how far an edge has traversed through the ring to generate the lower order bits, N[4:0], of the binary representation of the input voltage. NAND gates reset the ring in order to have it restart from a known initial state. This approach reduces the LSB of the A/D converter from an entire oscillation period to a single delay stage and reduces the counter's power consumption. So, while the previous design would require a 1-GHz oscillator for 10 bits of resolution at a switching period of 1-MHz, the oscillator in the new implementation only needs to oscillate at 32-MHz for the same resolution and switching frequency. It is important to point out here that this approach does not reduce the ring oscillator's power since it is set the by total switched capacitance and inverter delay, and not the oscillation frequency. Since the additional cost of the encoder block is small, this implementation enables low-power solution.

The A/D conversion techniques described thus far have been used to convert the output of the buck converter into a frequency and then into an equivalent digital representation of the voltage and frequency. Comparing this value to a reference determines whether the buck converter output voltage corresponds to the value required for the digital system to operate at the desired frequency of operation. If the reference is a

Figure 3.4. Low-power A/D converter

voltage, the difference between the outputs of two A/D blocks with the same counting interval generates a binary equivalent of the voltage difference. Good matching between the two oscillators ensures the regulated voltage matches the reference voltage. Given a frequency-locked loop, as described in Chapter 2, which assumes the reference is a clock frequency, the reference clock would feed straight into the counter and bypass the ring oscillator in the reference A/D path. In this case, the oscillator in the feedback path of the regulator must accurately model the critical path of the digital system to which power is delivered.

Given a digital representation of the difference between the regulated voltage and the reference, this error must then drive PID control blocks to servo the duty-cycle of the PWM rectangular wave to the buck converter, and drive the error to zero through negative feedback. A digital circuit equivalent of the PID control that operates on the error is covered next.

#### **3.2 Digital PID Control**

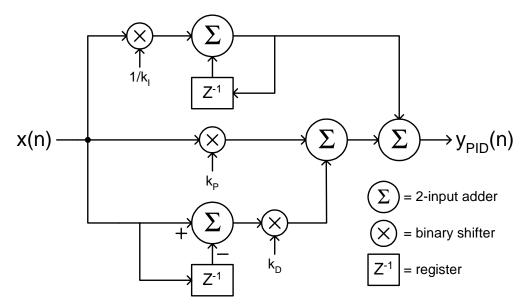

This section describes the digital implementation of the PID controller [49] that operates on the error generated by the A/D converters described above. Separate digital blocks implement the discrete-time equivalents of the proportional, integral and derivative functions of the controller. The output sum,  $y_{PID}$ , is a binary representation of the duty-cycle of the PWM rectangular wave that drives the buck converter. These digital blocks implement the following discrete-time functions:

$$y_P(n) = k_P \cdot x(n) \tag{3-4}$$

$$y_I(n) = y_I(n \to 1) + \frac{1}{k_I} x(n)$$

(3-5)

$$y_D(n) = k_D[x(n) \oplus x(n \oplus 1)]$$

(3-6)

$$y_{PID}(n) = y_P(n) + y_I + y_D(n)$$

(3-7)

x(n) represents the feedback error between the regulated output voltage and the reference at each discrete-time *n*. Each discrete interval *n* is equivalent to the switching period of the

Figure 3.5. Circuit implementation of PID control blocks

buck converter and control signals are pipelined through the digital blocks at this rate. The resulting discrete-time equivalents of the PID control blocks closely mimic the continuous-time transfer function, described in Chapter 2.

Detailed block diagrams of the three control blocks are presented in Figure 3.5. Since the update rate of the digital control is significantly lower than the rest of the digital system to which power is regulated, it has low performance requirements. Therefore, discrete-time control blocks utilize simple ripple-carry adders for addition and subtraction. Binary shifters implement multiplication and division, but limits multiplication and division to powers of 2, as follows:

$$k = 2^{N_{shift}}, (3-8)$$